**PROGRAM**

: NATIONAL DIPLOMA

ENGINEERING: ELECTRICAL

**SUBJECT**

: DIGITAL SYSTEMS 2

**CODE**

: EDS 231

DATE

: SUMMER SSA EXAMINATION 2017

13 JANUARY 2017

**DURATION**

: (SESSION 1) 08:00 - 11:00

WEIGHT

: 40:60

ASSESSOR

: Mr. V Rameshar

**MODERATOR** : Mr. D.R. Van Niekerk

**NUMBER OF PAGES** : PAGES 6

FULL MARKS

: 100

#### **INSTRUCTIONS TO STUDENTS**

- 1. ATTEMPT ALL QUESTIONS. 100 marks = 100%

- 2. THEORY TYPE QUESTIONS MUST BE ANSWERED IN POINT FORM BY CAREFULLY CONSIDERING THE MARK ALLOCATION.

- 3. ALL DIAGRAMS AND SKETCHES MUST BE DRAWN NEATLY AND IN PROPORTION.

- 4. ALL DIAGRAMS AND SKETCHES MUST BE LABELED CLEARLY.

- 5. ALL WORK DONE IN PENCIL EXCEPT DIAGRAMS AND SKETCHES WILL BE CONSIDERED AS ROUGH WORK.

- 6. NOTE: MARKS WILL BE DEDUCTED FOR WORK WHICH IS POORLY PRESENTED.

### **QUESTION 1**

- 1.1 Define the following terms with reference to TTL:

- 1.1.1 Noise margin

- 1.1.2 Speed/power relation

- 1.1.3 Fan-out

- 1.1.4 Sink current

- 1.1.5 Propagation delay time.

(5)

- 1.2 A certain gate draws 2 mA when its output is HIGH and 3.6 mA when its output is LOW. What is its average power dissipation if V<sub>CC</sub> is 5 V and the gate is operated on a 50% duty cycle? (5)

- 1.3 Determine the value for the pull-up resister for an open-collector gate if I<sub>OL(max)</sub>=40 mA and V<sub>OL(max)</sub>=0.25 V for each gate. Assume that 10 standard TTL unit loads are being driven from output X and the supply voltage is 5 V.

[16]

#### **QUESTION 2**

- 2.1 Explain the term 'retriggerable one-shot' and also show the result on a timing diagram. (3)

- An output pulse of 1000 ns duration is to be generated by a 74122 one-shot. Using a capacitor of 560 pF, determine the value of external resistance required.

(5)

2.3 Design and Sketch a one-shot, using a 555 timer that will produce a 0.25 s output pulse.  $(C_1 = 1 \mu F)$  (3)

[11]

## **QUESTION 3**

- 3.1 How does a synchronous counter differ from an asynchronous counter? (1)

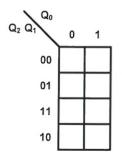

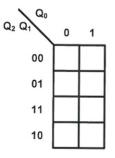

- Design a synchronous counter to produce the following binary sequence. Use J K flip-flops. Answer on the annexure sheet provided. 1, 4, 3, 5, 7, 6, 2, ...

(18)

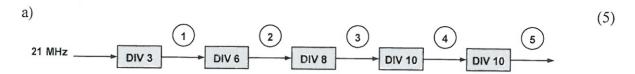

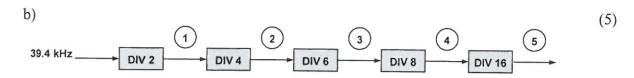

For each of the cascaded counter configurations, determine the frequency of the waveform at each point indicate by a circled number, and determine the overall modulus.

[29]

#### **QUESTION 4**

- 4.1 Why are shift registers considered as basic memory devices? (2)

- What is the storage capacity of a register that can retain two bytes of data? (2)

- 4.3 A divide-by-10 ring counter requires a minimum of:

- a) ten flip-flops

- b) five flip-flops

- c) four flip-flops

- d) twelve flip-flops (2)

- 4.4 Sketch the logic diagram for a four-bit Johnson counter and also Sketch the timing sequence for the counter. (Twisted ring). (10)

[16]

## **QUESTION 5**

- 5.1 The bit capacity of a memory that has 1024 addresses and can store 8 bits at each address is

- a) 1024

- b) 8192

- c) 8

- d) 4096 (1)

| 5.2        | A 32-bit data word consist of                                                       |     |

|------------|-------------------------------------------------------------------------------------|-----|

| a)         | 2 bytes                                                                             |     |

| b)         | 4 nibbles                                                                           |     |

| e)         | 4 bytes                                                                             |     |

| d)         | 8 bytes                                                                             | (1) |

| 5.3        | Data is stored in RAM during the                                                    |     |

| ı)         | read                                                                                |     |

| )          | enable                                                                              |     |

| 2)         | write                                                                               |     |

| d)         | addressing operation                                                                | (1) |

| 5.4        | Data that is stored at a given address in RAM is lost when                          |     |

| 1)         | power goes off                                                                      |     |

| )          | data is read from the address                                                       |     |

| <b>c</b> ) | new data are written at the address                                                 |     |

| d)         | both (a) and (c)                                                                    | (1) |

| 5.5        | A ROM is a                                                                          |     |

| 1)         | non-volatile                                                                        |     |

| )          | volatile                                                                            |     |

| :)         | read/write                                                                          |     |

| .)         | byte-organized memory.                                                              | (1) |

| .6         | The storage cell in a SRAM is                                                       |     |

| ı)         | a flip-flop                                                                         |     |

| )          | a capacitor                                                                         |     |

| )          | a fuse                                                                              |     |

| .)         | a magnetic domain.                                                                  | (1) |

| .7         | A DRAM must be                                                                      |     |

| )          | replaced periodically                                                               |     |

| )          | refreshed periodically                                                              |     |

| )          | always enabled                                                                      |     |

| )          | programmed before each use.                                                         | (1) |

| .8         | What is the <i>smallest unit</i> of information that can be stored in a memory? (1) |     |

| .9         | What is a write operation?                                                          | (1) |

| .10        | What is a <i>read</i> operation?                                                    | (1) |

|            | •                                                                                   |     |

| .11        | Describe the difference between a RAM and a ROM.                                    | (2) |

|            | Describe the refresh exercise in a DDAM                                             | (0) |

| 12         | Describe the refresh operation in a DRAM.                                           | (2) |

| <b>QUESTION</b> | 6 |

|-----------------|---|

|-----------------|---|

- 6.1 Sketch the R/2R D-A convertor <u>and</u> show its resistor ratios values. (6)

- Explain with the aid of sketches how the Successive-Approximation conversion process takes place when receiving an analog voltage of 5V on the input. (Use the Keep/Reset method).

(8)

[14]

TOTAL MARKS = 100

# **ANNEXURE**

## STUDENT\_SURNAME

**NEXT STATE TABLE**

| Present State<br>Q <sub>2</sub> Q <sub>1</sub> Q <sub>0</sub> |  | Ne<br>Q <sub>2</sub> | ext Sta<br>Q <sub>1</sub> | te<br>Q₀ |  |

|---------------------------------------------------------------|--|----------------------|---------------------------|----------|--|

|                                                               |  |                      |                           |          |  |

|                                                               |  |                      |                           |          |  |

|                                                               |  |                      |                           |          |  |

|                                                               |  |                      |                           |          |  |

#### TRANSMISSION TABLE

| Output State Transitions<br>(Present state to next state) |                | Flip-flop inputs |                               |             |             |   |

|-----------------------------------------------------------|----------------|------------------|-------------------------------|-------------|-------------|---|

| Q <sub>2</sub>                                            | Q <sub>1</sub> | Q <sub>0</sub>   | J <sub>2</sub> K <sub>2</sub> | $J_1$ $K_1$ | $J_0$ $K_0$ | - |

|                                                           |                |                  |                               |             |             |   |

|                                                           |                |                  |                               |             |             |   |

|                                                           |                |                  |                               |             |             |   |

|                                                           |                |                  |                               |             |             |   |

|                                                           |                |                  |                               |             |             |   |

|                                                           |                |                  |                               |             |             |   |

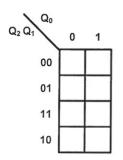

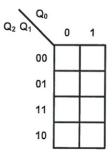

| $Q_2 \ Q_1 \\$ | 0 | 1 |

|----------------|---|---|

| 00             |   |   |

| 01             |   |   |

| 11             |   |   |

| 10             |   |   |