**PROGRAM**

NATIONAL DIPLOMA

CHEMICAL ENGINEERING

**SUBJECT**

PROCESS CONTROL

**CODE**

ICP3111

**DATE**

SUMMER EXAMINATION

**25 NOVEMBER 2016**

**DURATION**

08:30-11:30

**TOTAL MARKS**

100

**FULL MARKS**

100

**EXAMINER**

: MRS T MASHIFANA AND MS T SITHOLE

**MODERATOR**

: DR H RUTTO

**NUMBER OF PAGES**

:6 PAGES INCLUDING COVER PAGE

**INSTRUCTIONS:**

CALCULATORS ARE ALLOWED (ONE PER STUDENT)

NO COMPUTER ALLOWED

ANSWER ALL QUESTIONS

Question 1: [25]

1.1. What are the requirements to be satisfied to meet plant or process objectives? Provide examples to support your answer. [10]

1.2. Ethanol is feed to continuous reactor with presence of Acid Sulphuric catalyzer to produce ethylene. Distillation process then will be applied to separate ethylene-H<sub>2</sub>O mixture. Ethylene as a top product is then condensate with condenser to perform liquid ethylene. Hydrogenation of ethylene applies in another reactor with presence of Nickel catalyzer to produce ethane as a final product.

$$\begin{array}{c} \text{CH}_3\text{CH}_2\text{OH} & \xrightarrow{\text{H}_2\text{SO}_4} & \text{CH}_2\text{=CH}_2 + \text{H}_2\text{O} \\ \text{CH}_2\text{=CH}_2 + \text{H}_2 & \xrightarrow{\text{Ni}} & \text{CH}_3\text{CH}_3 \end{array}$$

(a) What is/are the reactant/s and the final product/s?

[3]

(b) List all the major equipment

[3]

(c) Develop a block flow diagram (BFD) for these processes.

[9]

Question 2 [20]

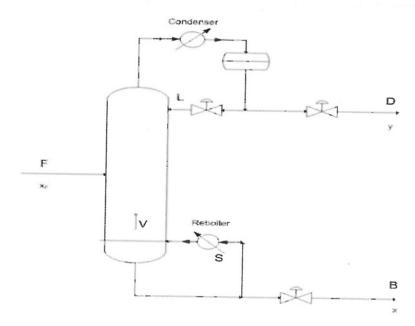

Figure 2 below shows a distillation column. The objective is to maintain the distillate composition flow rate back to the column at  $C_D$  and the flow rate in the tailings at  $F_T$

By following the control system design steps, show how you will implement a control system to achieve the objectives.

Figure 2: Distillation column

| Question 3                                | [20] |

|-------------------------------------------|------|

| 1. Draw a logic circuit for the following |      |

| (a) $F = (A+B).C$                         | [3]  |

| (b) $F = A + B.\overline{C + D}$          | [3]  |

| (c) $F = A.B + \overline{A.C}$            | [4]  |

| (d) $F = \overline{(A+B)}.(C+D).C$        | [5]  |

| A D' 1.1 1 1 1                            | - 1  |

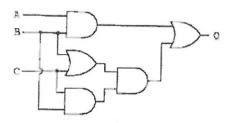

2. Find the behaviour expression or alarm setting output for the following circuit (Neatly copy the circuit and label each signal stream labelled and show the final expression Q. [5]

| Question 4 | [15] |

|------------|------|

| Question 4 | [15] |

A control with an equal percentage inherent characteric has a maximum Cv of 1300 and a rengeability of 40.

- (a) Calculate the % changes in the flow for every 10% change in valve. [5]

- (b) Calculate the values of Cv corresponding to valve travel from 10% to 40% by step of 10% draw a table containing these values. [10]

| Question 5                                                           | [20] |

|----------------------------------------------------------------------|------|

| (a) What are the types of error signal measurements? Give five       | [5]  |

| (b) What is the difference between an analogue and a digital signal? | [4]  |

| (c) Explain the two main categories of control valve?                | [4]  |

| (d) What are the uses of op-amps? Give four                          | [4]  |

| (e) Give three types of control valves?                              | [3]  |

Appendix A: Traditional digital logic gate symbols, Boolean functions and truth table

| Туре       | Distinctive<br>shape | Boolean algebra<br>between A & B | Meaning                                                       | Truth table                                                                                                                 |  |  |

|------------|----------------------|----------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|

| AND        | <del>_</del> D-      | $A\cdot B$                       | Output is true if and only if (iff) both $A$ and $B$ are true | INPUT OUTPUT A B A AND B O O O O 1 O 1 O O 1 1 1 1                                                                          |  |  |

| OR         | <b>→</b>             | A + B                            | True iff $A$ is true, or $B$ is true, or both.                | INPUT OUTPUT  A B A OR B  0 0 0  0 1 1  1 0 1  1 1 1                                                                        |  |  |

| NOT        | <b>-</b> >-          | $\overline{A}$                   | True iff $A$ is false.                                        | INPUT OUTPUT A NOT A 0 1 1 0                                                                                                |  |  |

| NAND       | _>-                  | $\overline{A\cdot B}$            | A and $B$ are not both true.                                  | INPUT     OUTPUT       A     B     A NAND B       0     0     1       0     1     1       1     0     1       1     1     0 |  |  |

| <u>NOR</u> | <b>→</b>             | $A + \overline{B}$               | True iff neither $A$ nor $B$ .                                | INPUT OUTPUT A B A NOR B 0 0 1                                                                                              |  |  |

|      |          |                        |                                    | 0 1 1            | 1 0 1              | 0 0 0                  |

|------|----------|------------------------|------------------------------------|------------------|--------------------|------------------------|

| XOR  | <b>⇒</b> | $A \oplus B$           | True iff $A$ is not equal to $B$ . | IN A 0 0 1 1 1   | _                  | OUTPUT A XOR B 0 1 1 0 |

| XNOR | <b>⇒</b> | $\overline{A\oplus B}$ | True iff $A$ is equal to $B$ .     | 0<br>0<br>1<br>1 | PUT  B  0  1  0  1 | OUTPUT A XNOR B 1 0 1  |